## 3入出力2状態可逆論理素子の万能性 —ロータリー素子の直接的構成法—

Universal reversible logic elements with 3 inputs, 3 outputs and 2 states

-Direct composition method of a rotary element-

上野 亮一 · 森田 憲一 Ryoichi Ueno, and Kenichi Morita

広島大学大学院工学研究科

Graduate School of Engineering, Hiroshima University

#### 概要

可逆論理素子という,素子の状態と出力から入力と前時刻の素子の状態を一意に決定できる論理素子を扱う。この素子を組み合わせれば,可逆的な計算システムを構成できる。そして,可逆的な計算過程を物理的に可逆な過程によって適切に実現した場合,計算に要するエネルギーを任意に小さくできることが知られている。本研究では,その素子のみで任意の順序機械を構成できるという性質である「論理万能性」を持つ可逆論理素子について考察する。従来の研究では,各4本の入出力線,2つの状態を持ち,万能性を有する可逆論理素子,ロータリー素子が提案されている。その素子自体の単純化を考え,各3本の入出力線,2つの状態を持つ可逆論理素子を用いて,ロータリー素子を構成する。3入出力2状態可逆論理素子は24種類の同値類に類別でき,その中で論理万能性を有するFredkinゲートを構成できるものは14種類であることがOgiroらによって示されている。それら14種類の中で6種類については,これまでにロータリー素子が直接構成できることが分かっていたが,今回さらに,4種類についてロータリー素子を直接構成できた。ロータリー素子と同等の能力を持つ可逆論理素子を見出すことで,将来,素子の物理的実現を目指す際の手がかりが得られると考えられる。

キーワード: 可逆コンピューティング, 可逆論理素子, ロータリー素子 Keywords: reversible computing, universal reversible logic element, rotary element

### 1 まえがき

ここでいう可逆な計算システムとは、そのシステムのどの計算状況もその直前の時刻にとり得る計算状況を高々一つしか持たない、つまりその計算過程を一意に逆戻りできるようなものを指す、それに対し、普通の計算システム、たとえば現在のコンピュータなどはメモリの内容を消去したり、状態を忘却したりできるので一般には非可逆である。可逆な計算システムの特徴として、チューリングマシンや論理回路など

においては、システムに可逆性の制約を付加しても計算能力が下がらないことがある。さらに、可逆コンピューティングにおける計算過程は情報の消去を伴わないため、適切な物理的実現をした場合、エネルギーの消費を非常に小さくすることが原理的に可能である[1].

Fredkin と Toffoli [2] は Fredkin ゲートと呼ぶ可逆論理素子が万能である(それを用いて任意の順序機械を構成できる)ことを示した。また Morita [3] は、ロータリー素子とよぶ、1 ビットのメモリを持つ可逆論理素子を提案し、その万

能性を示した.前者は純粋のゲートであるため, 2つ以上の入力信号の同期をとるためのクロック が不可欠であるのに対し,後者は1つの入力信 号とメモリに蓄えられた情報とが相互作用する ので同期機構が不要となる.このため,ロータ リー素子を用いて適切に設計すると回路の構成 が非常に単純になる.

本研究ではロータリー素子よりも単純な3入 出力2状態素子について扱う.3入出力2状態素 子は数多くあるが、過去の研究において24の同 値類に類別できることが知られている[4]. さら に、その24種類中で本質的に3入出力2状態で あるものは14種類である(他は状態が変化しな いものや本質的に2入出力と同じものである). そして、14種類すべてにおいて Fredkin ゲート を構成できることが示されている[4]. Fredkin ゲートは万能なので、14種類の3入出力素子は Fredkin ゲートを介してロータリー素子を構成で きる. しかし、Fredkin ゲートを介して構成する と同期機構が必要となりロータリー素子の利点 が失われてしまう。よって、3入出力素子でロー タリー素子を直接 (Fredkin ゲートを介さずに) 構成する必要がある. 現在, ロータリー素子を 直接構成できるものはまだ6種類しかわかって いない. すべてにおいて構成可能かどうかわか れば、どの3入出力素子が実現できてもロータ リー素子と同じ働きができる. 今回は新たに4 種類の素子でロータリー素子を構成できたので その結果を示す.

### 2 従来の万能可逆論理素子

本章では、万能性を有する可逆論理素子として最もよく知られている Fredkin ゲート [2], および、過去の研究の4本の入出力線、2つの状態を持つ可逆論理素子で万能性を有するロータリー素子 [3] を紹介する.

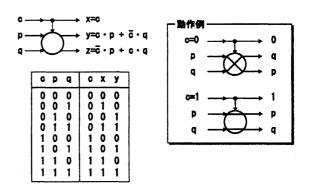

#### 2.1 Fredkin ゲート (F-ゲート)

F-ゲートは図1のような3本の入出力線を持つゲートである. F-ゲートの動作は,入力線cに入力の値によって,残りの2つの入力線p,qをどの出力線に接続するかを制御できるというものである.入力線cに入力1があると,入力線p,qは平行に出力線と接続される.すなわち,入

力線pは出力線xに,入力線qは出力線yに接続される.一方,入力線cに入力0が与えられた場合,入力線p,qは交差して出力される.すなわち,入力線pは出力線yに,入力線qは出力線xに接続される.図1左下の表は,この動作を真理値表で表したものである.この素子はAND,NOT,FANOUT の3つのゲートを構成できるため,任意の順序機械を構成できる.つまり,万能である.

F-ゲートは3つの入力c, p, qが同時に行われ,同時に出力される.このことから,F-ゲートを扱うには,入力パルスの同期をとるためのクロックが不可欠になる.

図 1: F-ゲートとその動作

#### 2.2 ロータリー素子

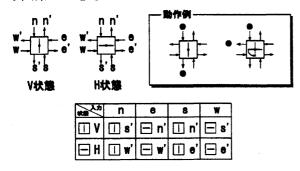

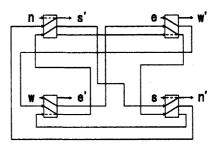

ロータリー素子は概念的には図2のように、内部の回転羽根の向きで示される H 状態と V 状態の 2 状態をもつ4 入出力の論理素子である. これらの2つの内部状態により、1 ビットのメモリを表現することができる. H 状態のときに左右から, V 状態のときに上下から信号が入力されると、信号は羽根と平行なためそのまま直進し、状態は変化しない. 一方、H 状態のときに上下から、V 状態のときに左右から信号が入力されると、信号は羽根と垂直なため右折し、羽根は 90°回転し状態変化を起こす.

このような動作は、図2のような遷移関数表で定義される。可逆論理素子の遷移関数表は、現在の素子の内部状態と入力線の組み合わせが次の時刻の内部状態と出力線の組み合わせと1対1対応になるように記述される。この1対1対応であることで、内部状態と出力先から前時刻の内部状態と入力位置を一意に決定できるので

ある. 実際,図2の遷移関数表に関して,内部状態 V, H と出力線 n', e', s', w' の組み合わせが,どの内部状態 V, H と入力線 n, e, s, w の組み合わせに対して重複していない. よって,ロータリー素子は可逆論理素子である.ロータリー素子は、高々1入力線にしか入力が与えられないとしている.つまり、F-ゲートに比べ、ロータリー素子は入力信号の同期をとるクロック機構を必要としないという長所を有する.さらに、図20のようにロータリー素子だけを使って可逆チューリングマシンを構築できることが分かっている[3].

ロータリー素子のもう一つの特徴として、ビリヤード・ボール・モデル (BBM) によって非常に簡単に実現できる. BBM とは弾性衝突をももである [2]. BBM は、2次元空間を摩擦なしに運動するボールと、その軌道を変えるたら構立に置くことのできる反射板を配置に置くことがものとうにが出たを表している。図3のようにボールときるの以前にあるときがH状態を表してがあるときがH状態を表してが出たとき、同じ速度でボールが出たとき、同じ速度でボールが出た。より、内部でのエネルギー損失が0であるような回路ができる.

図 2: ロータリー素子とその動作

図3において、V 状態のときにs から入力があった場合は、状態を保持するボールと入力のボールが接触しない。よって状態が変化せずにn' から出力される。また、H 状態のときにs から入力があった場合は、状態を保持するボールと入力のボールが衝突する (図4)。さらにもう一回衝突して一方のボールはV の位置に停止し、

もう一方のボールは e' から出力される (図 5). これにより図 3 の BBM はロータリー素子を構成できていることがわかる.

図 3: BBM によるロータリー素子の実現

図 4: BBM によるロータリー素子の実現: [H 状態, 入力 s]

図 5: BBM によるロータリー素子の実現: [H 状態, 入力 s] → [V 状態, 出力 e']

# 3 3入出力2状態可逆論理素子によるロータリー素子の構成

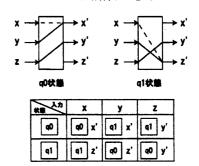

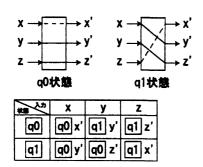

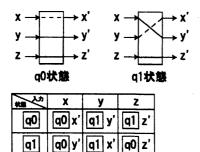

本研究では、先述のロータリー素子のような4入出力2状態可逆論理素子の単純化を考え、入出力線数が3、状態数が2である可逆論理素子全てのうち、ロータリー素子を構成できるものを探す。3入出力2状態可逆論理素子は、状態集合を $\{q_0,q_1\}$ 、入力記号集合を $\{x,y,z\}$ 、出力記号集合を $\{x,y,z\}$ 、出力記号集合を $\{x',y',z'\}$ とするとき、 $\delta:\{q_0,q_1\}\times\{x,y,z\}\rightarrow\{q_0,q_1\}\times\{x',y',z'\}$ なる可逆順序機械である。このような単射は単純計算では $(3\times2)!=720$ 種類存在する。このような素子の中で、入力線及び出力線を入れ替えたものなどを同値類としてまとめると、図6のように24種類に分類できることが分かっている。

今回はその中で 素子 3-60, 素子 3-64, 素子 3-65, 素子 3-90 (色付けしてあるもの) について 考える. これらの素子の番号は, [4] の論文内で 同値類の分類のためにコンピュータで 720 個の素子すべてに付与されたものである.

| 3-95       | 茅    | ä        | 3-18        | <b>并</b>  | <b>*</b> |

|------------|------|----------|-------------|-----------|----------|

| <b>₹</b>   | 松    | #        | <b>₹</b>    | <b>₹</b>  | #        |

| 3-450      | §#   | 李        | * <u>*</u>  | "·<br>王   | #        |

| #          | Œ    | \$       | **          | <b>\$</b> | ₹        |

| 3-451<br>± | 3-91 | 3-63     | <u>}221</u> | 莽         | #        |

| <br>₹      | *    | <b>₹</b> | #           | <b>₹</b>  | <b>₹</b> |

| 3-453      | 3-94 | ·<br>本   | 3-23        | <b>进</b>  | 3-6      |

|            | #    | #        | **          | #         | ₹.       |

図 6: 3入出力 2 状態可逆論理素子の各同値類 の代表元

## 3.1 素子 3-60 によるロータリー素子の構成。

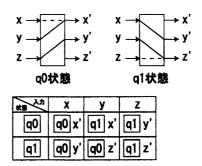

素子 3-60 は図 7 のような  $q_0$  状態と  $q_1$  状態をもつ,3 入出力 2 状態の論理素子である.信号が入力されるとそれぞれに対応した線を通り出力される.実線を通るときは状態を変化させ、破線を通るときは状態を変化させない.この素子が可逆であることは図 7 の遷移表が 1 対 1 対応

であることからわかる.

図 7: 素子 3-60 とその動作

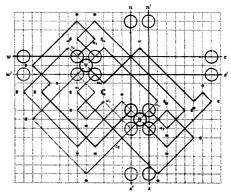

図8のように素子 3-60 のみを用いてロータリー素子を構成できる。これはロータリー素子のV状態を表している。H状態は図中の素子の状態をすべて逆にすればよい。素子 3-60 を使うと、今までの結果に比べて非常に少ない素子数でロータリー素子を構成することができた。

図 8: 素子 3-60 によるロータリー素子の実現

## 3.2 素子 3-64 によるロータリー素子の構成

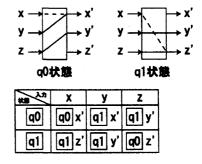

素子 3-64 は図 9 のような  $q_0$  状態と  $q_1$  状態をもつ,3 入出力 2 状態の論理素子である.この素子が可逆であることは図 9 の遷移表が 1 対 1 対応であることからわかる.

図 9: 素子 3-64 とその動作

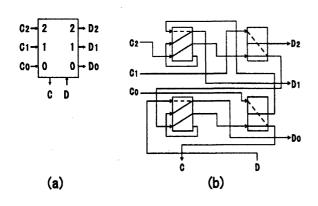

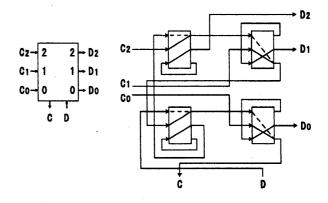

ここでロータリー素子の構成を簡単にする coding-decoding (CD) module [5] について説明 する. CD module とは4つの入力線 $C_0$ ,  $C_1$ ,  $C_2$ , D, 4つの出力線 $D_0$ ,  $D_1$ ,  $D_2$ , C, そして3つの 状態0, 1, 2 を持つ素子である(図 10(a) 参照). 初期状態は0 で,この状態以外では $C_0$ ,  $C_1$ ,  $C_2$  から入力されない。0 状態で入力線 $C_i$  ( $i \in 0$ , 1, 2) に信号がきたとき,状態は0 からi に変化し、C から出力される。その後,入力線D に信号がくると $D_i$  から出力され状態はi から0 に戻る。この素子には同時に高々1 つの信号しか入らない。そして素子3-64 によってCD module を構成したものが図 10(b) である.

図 10: 素子 3-64 による CD module の実現

CD module を使うと、図 11 のように素子 3-64 のみを用いてロータリー素子を構成できる.これはロータリー素子の V 状態を表している.H 状態は図中の CD module 以外の素子の状態をすべて逆にすればよい.

図 11: 素子 3-64 によるロータリー素子の実現

## 3.3 素子 3-65 によるロータリー素子の構成

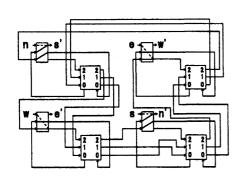

素子 3-65 は図 12 のような  $q_0$  状態と  $q_1$  状態をもつ,3 入出力 2 状態の論理素子である.この素子が可逆であることは図 12 の遷移表が 1 対 1 対応であることからわかる.図 13 のようにこの素子でも CD module を構成できる.

図 12: 素子 3-65 とその動作

図 13: 素子 3-65 による CD module の実現

図 14: 素子 3-65 によるロータリー素子の実現

図 14 のように素子 3-65 のみを用いてロータリー素子を構成できる. これはロータリー素子のV状態を表している. H状態は図中のCD module 以外の素子の状態をすべて逆にすればよい.

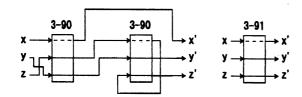

## 3.4 素子 3-90 によるロータリー素子の構成

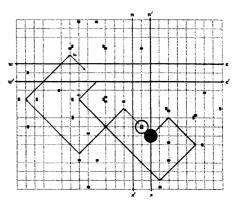

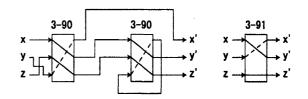

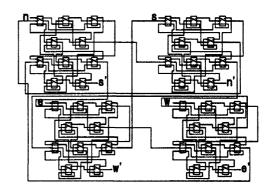

ここでは今までと違い、3入出力2状態可逆 論理素子で他の3入出力2状態可逆論理素子を 構成し、ロータリー素子を構成できることを示す。素子3-90を2個使って素子3-91を構成できることを示ることは過去の研究より分かる(図17)[6]. さらに、素子3-91が素子数40でロータリー素子を 構成できることが分かっているので(図19)[7]、素子3-90を80個使えば、ロータリー素子を構成できることが示せる。図19はロータリー素子のV状態を表している。H状態は色のついた8個の素子の状態をすべて逆にすればよい。

図 15: 素子 3-90 とその動作

図 16: 素子 3-91 とその動作

図 17: 素子 3-90 による素子 3-91 の実現 ( $q_0$  状態)

図 18: 素子 3-90 による素子 3-91 の実現 (q1 状態)

図 19: 素子 3-91 によるロータリー素子の実現

#### 4 むすび

今回は、3入出力2状態素子の素子3-60、素子3-64、素子3-65、素子3-90によってロータリー素子を構成した。今後の課題としては、これら以外の3入出力の論理素子でロータリー素子を構成できないかを検討する。現在、ロータリー素子を構成できると証明されたものは今回の結果を含めて10個ある。そして、構成不可能であると証明されたもの(状態が変化しないもの)は6個。さらに、構成不可能であると予測されているもの(2入出力と同じもの)が4個ある。今後はそれ以外の残りの4個の素子について検討する。

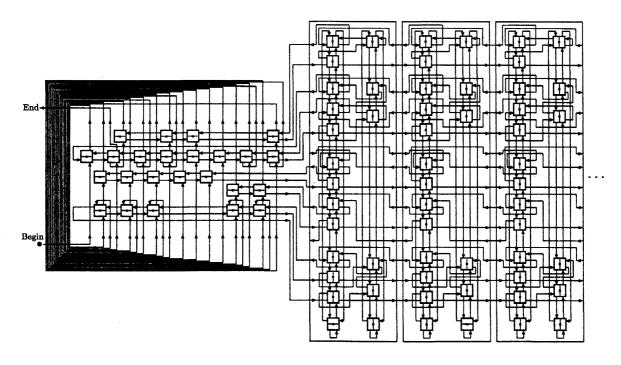

図 20: ロータリー素子による可逆チューリング マシンの構成例 [3]

### 参考文献

- Bennett, C. H., Logical reversibility of computation, IBM J. Res. Dev. Vol. 17, No.6. pp. 525-532 (1973).

- [2] Fredkin, E., and Toffoli, T., Conservative logic, Int. J. Thoeret. Phys., 21, 219-253 (1982).

- [3] Morita, K., A simple universal logic element and cellular automata for reversible computing, Proc. 3rd Int. Conf. Machines, Computations, and Universality, Chisinau, LNCS-2055, 102-113 (2001).

- [4] Ogiro, T., Kanno, A., Tanaka, K., Kato, H., and Morita, K., Nondegenerate 2-state 3-symbol reversible logic elements are all universal, Int. Journ. of Unconventional Computing, Vol. 1, 47-67 (2005).

- [5] Lee, J., Peper, F., Adachi, S., and Mashiko, S., On reversible computation in asynchronous systems, Technical report of NICT (2003).

- [7] 藤川 真治, ロータリー素子を構成可能な3 入出力2状態可逆論理素子, 広島大学卒業 論文(2004).